One-Stop-Services für die elektronische Fertigung helfen Ihnen dabei, Ihre elektronischen Produkte einfach aus PCB und PCBA herzustellen

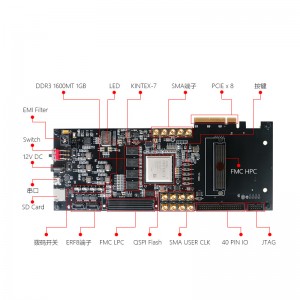

FPGA Xilinx K7 Kintex7 PCIe Glasfaserkommunikation

- DDR3 SDRAM: 16 GB DDR3 64-Bit-Bus, Datenrate 1600 Mbit/s

- QSPI Flash: Ein Stück 128-Mbit-QSPIFLASH, das für FPGA-Konfigurationsdateien und die Speicherung von Benutzerdaten verwendet werden kann

- PCLEX8-Schnittstelle: Die Standard-PCLEX8-Schnittstelle dient zur Kommunikation mit der PCIE-Kommunikation des Computer-Motherboards. Sie unterstützt den PCI Express 2.0-Standard. Die Einkanal-Kommunikationsrate kann bis zu 5 Gbit/s betragen.

- USB-UART-Serieller Anschluss: Ein serieller Anschluss, der über das Mini-USB-Kabel mit dem PC verbunden wird, um eine serielle Kommunikation durchzuführen

- Micro SD-Karte: Microsd-Karte Sitz ganz, können Sie die Standard-Microsd-Karte anschließen

- Temperatursensor: ein Temperatursensorchip LM75, der die Umgebungstemperatur rund um die Entwicklungsplatine überwachen kann

- FMC-Erweiterungsport: ein FMC HPC und ein FMCLPC, die mit verschiedenen Standard-Erweiterungskarten kompatibel sein können

- ERF8-Hochgeschwindigkeits-Anschlussterminal: 2 ERF8-Ports, die die Ultrahochgeschwindigkeits-Signalübertragung unterstützen. 40-Pin-Erweiterung: Reserviert eine allgemeine Erweiterungs-IO-Schnittstelle mit 2,54 mm 40 Pin, effektives O hat 17 Paare, unterstützt 3,3 V

- Die periphere Verbindung des Pegels und des 5V-Pegels kann die peripheren Peripheriegeräte verschiedener allgemeiner 1O-Schnittstellen verbinden

- SMA-Anschluss; 13 hochwertige vergoldete SMA-Köpfe, die für Benutzer praktisch sind, um mit Hochgeschwindigkeits-AD/DA-FMC-Erweiterungskarten zur Signalerfassung und -verarbeitung zusammenzuarbeiten

- Taktverwaltung: Mehrere Taktquellen. Dazu gehört die 200 MHz System-Differenztaktquelle SIT9102

- Differenzieller Quarzoszillator: 50 MHz Quarz und programmierbarer Taktmanagement-Chip SI5338P: ebenfalls ausgestattet mit

- 66 MHz EMCCLK. Kann sich genau an unterschiedliche Taktfrequenzen anpassen

- JTAG-Anschluss: 10 Stiche 2,54 mm Standard-JTAG-Anschluss, zum Herunterladen und Debuggen von FPGA-Programmen

- Sub-Reset-Spannungsüberwachungschip: Ein Stück ADM706R-Spannungsüberwachungschip, und die Taste mit der Taste liefert ein globales Reset-Signal für das System

- LED: 11 LED-Leuchten, zeigen die Stromversorgung der Platine, config_done-Signal, FMC

- Betriebsanzeigesignal und 4 Benutzer-LED

- Taste und Schalter: 6 Tasten und 4 Schalter sind FPGA-Reset-Tasten,

- Programm B-Taste und 4 Benutzertasten bestehen aus 4 Einzelmesser-Doppelumschaltern

Schreiben Sie hier Ihre Nachricht und senden Sie sie an uns

Produktkategorien

-

Telefon

-

E-Mail

-

Whatsapp

-

Skype

-

Skype

-

Skype